*  This post is also available in English.

This post is also available in English.

Contenu

* Introduction

* Matériel : Le ircuit

** Composants

** Breadboard (planche à pain)

** Choix des ports GPIO et de leur broches sur la carte

** partie LED

** Résistances

** Partie bouton

* Le logiciel

** Initialisation

** Boucle principale

** Routine de Service d’intérruption (ou ISR, Interrupt Service Routine)

** Supprimer l’effet de rebond (Debouncing)

*** Chronomètre ESP

↑ Introduction

Mise à jour: J’ai écris, à la suite de cet article, un autre enseignant l’utilisation d’un potentiomètre et d’un écran OLED..

Suite à la mise à jour d’ArchLinux de python 3.9 vers 3.10, les outils ont du être réinstallés en effectuant :

cd ~/esp/esp-idf

git pull

git submodule update --init --recursive

./install.sh esp32c3

Si vous n’avez jamais utilisé ESP-IDF, vous pouvez lire l’article précédent, d’introduction à ESP-IDF sur les ESP32-C3 basées sur du RISC-V, comment l’installer et lancer l’environment pour compiler et flasher le code. J’ai également écrit un article à propos de l’utilisation d’ESP32-C3 avec le système embarqué POSIX, Apache NuttX , mais il sera inutile ici.

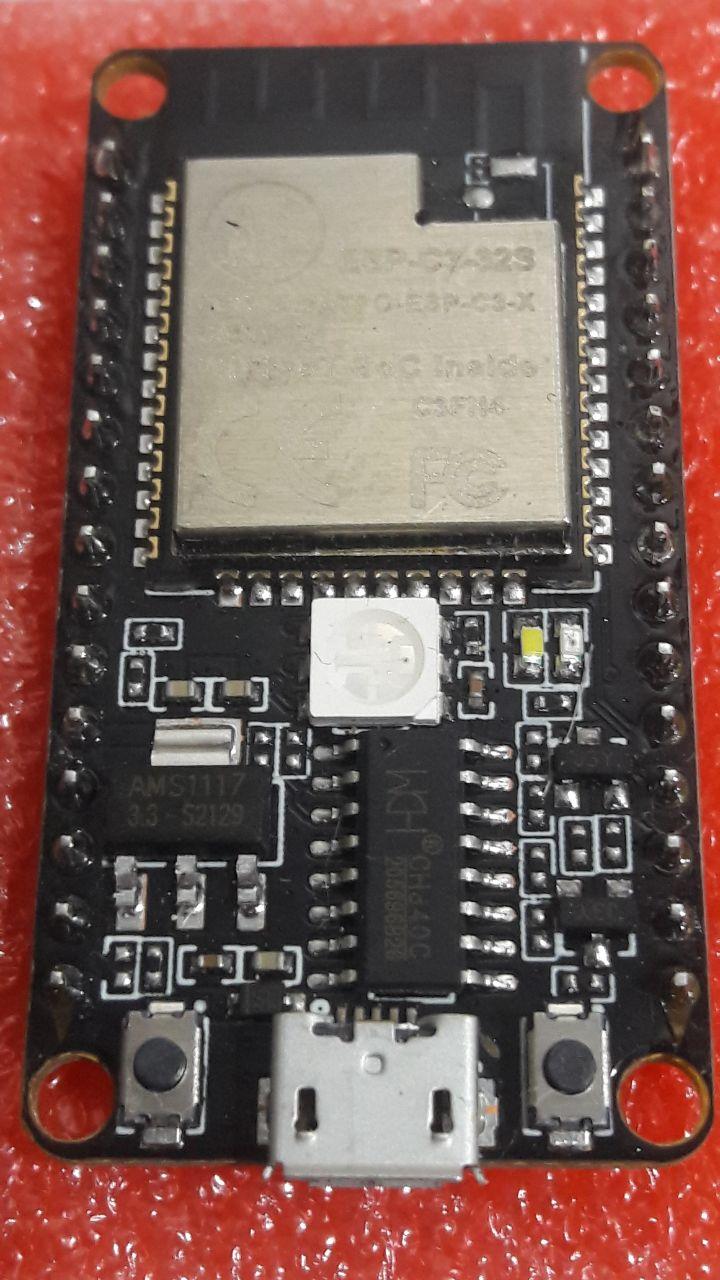

Cet article concerne, à propos le développement, sur ESP32 (plus spécifiquement sur une carte NodeMCU basée sur un ESP32-C3 à moins de 3.5 €, mais il devrait fonctionner à peu près à l’identique sur les autres cartes basées sur de l’ESP) :

* Comment faire clignoter une LED externe en utilisant les ports dits GPIO, en expliquant comment déterminer la tension (en volts, V) et l’intensité (en ampères, A) nécessaires au fonctionnement de la LED, ainsiq que le calcul de la résistance nécessaire, par différents moyens.

* Des explications sur les bandes de couleur des résistances et le calcul des résistances montées en parallèles. Je donne également un lien vers un logiciel libre et à source ouverte que j’ai écrit, pour aider à calculer les résistances nécessaires (en fonction du type de LED, et de l’intensité désirée).

* Comment connectet un commutateur externe aux probches GPIO, et la résistance nécessaire. Comment recevoir et gérer de la bonne façon son état. Notamment en supprimant l’effet de rebond, (debouncing) liée à la pression physique d’un humain sur le bouton, ainsi que l’utilisationd el’interruption logicielle (c’est une tâche plus facile qu’il n’y paraît).

* Comment faire clignoter la LED RVB incluse et l’arrếter/démarraer en utilisant un interrupteur, de façon asyncrone.

Continue reading →

Table of Content

Table of Content