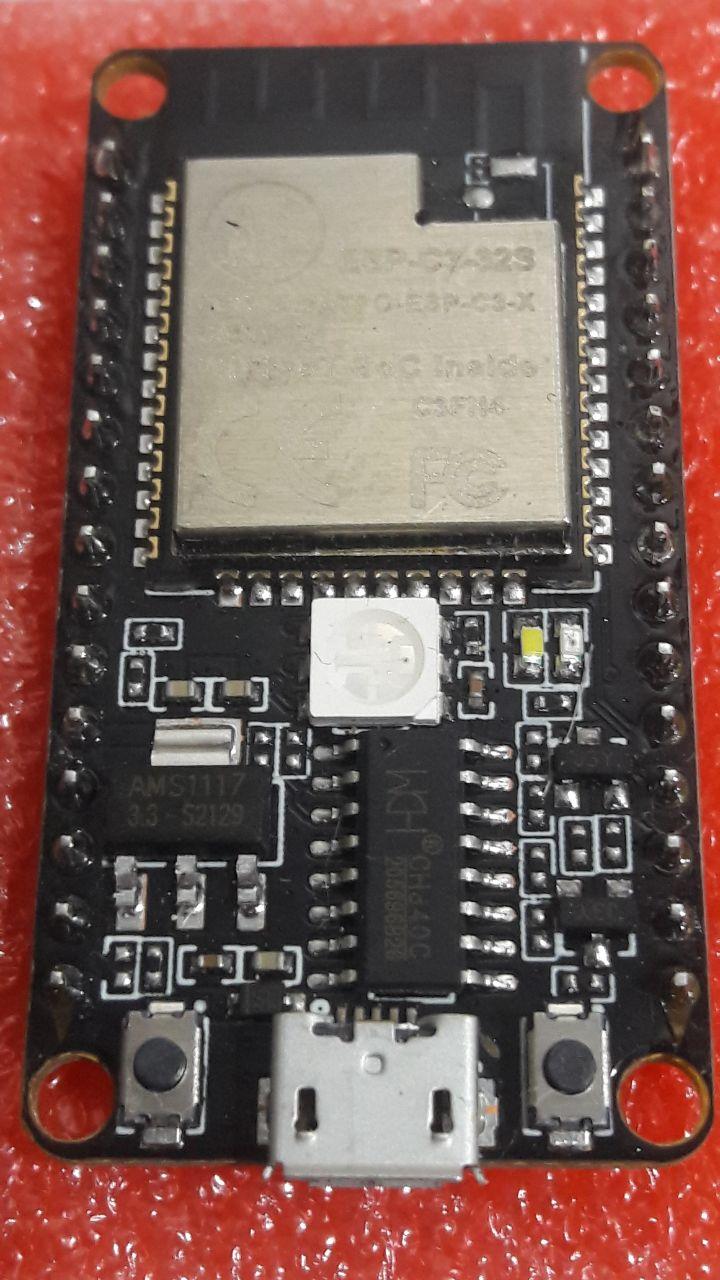

* Introduction The list of existing ESP32-C3 SoC modules (with their specs) is very interesting, This one RISC-V core SoC has lower computing power than the ESP32-S3 (dual-core Xtensa ISA based, with a RISC-V co-processor core for “ultra low power” (ULP) mode), but RISC-V architecture is also far more efficient and will for sure have longer lifetime support and evolution due to its openness. ESP32-C3 use an RV32IMC (Integer, Multiplication/division and Compressed extensions) core. I bought for my test a ESP-C3-32S-Kit on AliExpress (for ~3.4€). There is also an interesting option, where you can use really tiny 3~4 € ESP-C3-01M-Kit programmer interface/mother board, with a SoC included alone on a daughter (ESP32-C3M with an on PCB antenna). This allows, to flash several pads one only one programmer board. This reduce size of the needed system for final application to just the SoC and it’s power supply and peripherals. Pads of the SoC daughter board are wide enough to be easily soldered. ESP-IDF is a tool to develop in C language on Espressif platforms, including ESP8266 and ESP32 series. It uses FreeRTOS free and open source embedded real-time OS for its SoCs. Sadly the official documentation for installing it is incomplete with the current state (November 2021) of GIT repository. Here is the mean to install a working ESP-IDF for this SoC series on Linux. This will be more compact and straight forward that the official with Linux+Windows installation. About RISC-V more generally, I created this week a list of available Open Source RISC-V implementations, and open sources tools to build them or work with them. Continue reading  Table of Content

Table of Content

* Step 1, install dependencies

* Step 2, install ESP-IDF

* Step 3, setup working environment

* Step 4, test “Hello World” example

* Step 5, tune the target, if needed

* Step 6, flash the project

* Step 7, viewing the output

* Troubleshooting

** Invalid value for ‘{esp32|esp32s2}’: ‘esp32c3′ is not one of ‘esp32′, ‘esp32s2′

** libsodium/crypto_box/curve25519xchacha20poly1305/box_seal_curve25519xchacha20poly1305.c

** Flashing errors

*** Detection, power, and device that disappear

*** usbfs: interface 0 claimed by ch341 while ‘brltty’ sets config #1

** Problem with CA certificates bundleIntroduction

Category Archives: RISC-V

Short and practical introduction to FPGA, Verilog and Verilator and few words about SystemVerilog

Warning, I’m a less than one month beginner in Verilog, Verilator et FPGA, studied as a hobby, if there are some mistakes I will correct it. You can contact me on The Fediverse.

Table of Content

* Introduction

** Real world full process

** Things to know and understand

** How to code a FPGA

* Verilog

** Values

** Types

** Gates

** Modules

** Simple example, writing an “and” gate

** Initial and always blocks

* Simple example with Verilator

** Make the test with Verilator

** Tracing example and GTKWave

** About Verilator examples

** Basic practical example with Verilator

* Further reading

The text in strong are here to help diagonal reading.

Introduction

Still continue to go to lower layers with the world of FPGA (Field Processors Gateway Array). This is a reprogrammable development electronic tool used to build and test processor. After the processor is validated in FPGA, you can start to build ASIC (Application-specific integrated circuit), actual hardwired processors that we use every-days in our computing devices. FPGA are also used as is in several industrial appliance (avionics, audio or video processing, etc…) for their parallelism, so the fact they are faster than a general purpose ASIC and a piece of software in these cases, and the ability to update them easily in case of problem. This post is a little introduction about FPGA, the popular IEEE standard Verilog HDL (“Hardware description language”) language and how to test it with free and open source software (FOSS) Verilator simulator. If you want to use VHDL, GHDL is FOSS simulator for VHDL.

64x64x16colours (Sweetie16) PixelArt with Pixelorama “β-karoten – We know whom will be eat”

I participated to the LoveByte Battleground demoparty> that runned this week-end, by posting a drawing last week. Sadly/funnily , there was few mistake ^^:

* I made a 64×64 pixels picture instead of a 128×128 one. The palette for the competition was 16 colours Sweetie16 (the default one on FOSS, TIC-80 fantasy console (Source code)).

* My second mistake is I’ve uploaded a first version, and few hours later another one using (FOSS) source code) on Debian on (FOSH) RISC−V (Specifications, there are lot of free or not implementations) emulator of FOSS Qemu (Source code, Git instance), the first upload worked fine but the second one didn’t work (maybe because my installation of Netsurf doesn’t manage javascript)^^. I also performed in a livecoding match (256 bytes and 25 minutes limits). Result of my poor production, Commented Live coding session record.

This is made with FOSS Pixelorama (Source code), itself made on FOSS Godot game engine (Source code). I use FOSS Arch Linux OS. Also made a ArchLinux AUR package pixelorama-git after pixelorama package (for git version, I would like to use v0.9, still not out, only v0.8 was available). There are pixelorama package (last stable, compiling from source), and pixelorama-bin package (from developers binary tarball). Pixelorama is a Pixel art picture and animation editor. I believe I discovered Pixelorama thanks to blog Librearts.org.

The name is “β-karoten – We know whom will be eat”.

![]()

Screenshot of Pixelorama

Linux syscall and RISC-V assembly

Syscall in Linux kernel, is an interface to access to kernel basic functions. They are described in section 2 of man pages. The introduction is in man 2 syscall (indirect system call), and the list of functions are described in man 2 syscalls. Update: System Calls in lectures of official Linux kernel documentation including “Linux system calls implementation”, “VDSO and virtual syscalls” and “Accessing user space from system calls”

This article follow previous one about RISC-V overall progress and available tools to play with, I will try to make a short article here about Linux syscall usage and the RISC-V assembly case.

Table of Content

* Description section of the man page

* Getting the list of function and how to access them

* Passing parameters

* Function number and registers of return values

* Return values and error code

* Compiling and executing on virtual environment

* Update: Bronzebeard assembler and its baremetal environment for real hardware

RISC-V overall progress

WordPress is so cumbersome (brut long text in SQL DB and other misconception (WTF?), buggy (especially to multilingual content missing) and hard to maintain on long term that I didn’t posted for long time I want to migrate. You can test the new log engine (here specialised in TIC-80 256 bytes code on https://256b.popolon.org/.

I continued my travel toward RISC-V I started as said in a previous post in may 2018.

RISC-V Benefits

Among the benefit of RISC-V beside other implementations:

* Open source and without license fee availability, allowing everyone to participate, implement and have full specifications

* Highest modularity for a processor in specifications, You can reduce the core to only the set of functions you want for a specific tasks, allowing less transistor/more compact specialized cores, and then multiply cores with some specialized in some kind of tasks.

* Vector extension